**Application Note**

# Support for TE0821 modules with Vitis AI 3.0 DPU

Jiří Kadlec, Zdeněk Pohl, Lukáš Kohout, kadlec@utia.cas.cz, zdenek.pohl@utia.cas.cz, kohoutl@utia.cas.cz

### **Revision history**

| Rev. | Date      | Author | Description                             |

|------|-----------|--------|-----------------------------------------|

| v01  | 1.2.2024  | J.K    | Initial release                         |

| v02  | 2.2.2024  | J.K    | Manual creation of extensible platform  |

| v03  | 20.2.2024 | J.K    | Added fast track script, 3 module types |

| v04  | 17.2.2025 | J.K.   | Modified references                     |

### Contents

| 1 | Introduction                                                  | 1  |

|---|---------------------------------------------------------------|----|

|   | 1.1 Low cost systems used by UTIA in EECONE T4.3 and T4.4     | 2  |

|   | 1.2 Module based systems used by UTIA in EECONE T4.3 and T4.4 | 3  |

|   | 1.3 Objective of This Application Note and Evaluation Package |    |

| 2 |                                                               | 5  |

|   | 2.1 Reference HW for TE0821 module                            |    |

|   | 2.2 Create Extensible Platform HW                             |    |

|   | 2.3 Fast Track for Creation of Extensible platform HW         | 22 |

|   | 2.4 Validate Design                                           |    |

|   | 2.5 Compile Created HW and Custom SW with Trenz Scripts       |    |

|   | 2.6 Copy Created Custom First Stage Boot Loader               |    |

| 3 | 5 11                                                          |    |

|   | 3.1 Vitis AI 3.0 support                                      |    |

|   | 3.2 Building Petalinux for Extensible Design Flow             |    |

|   | 3.3 Disable CPU IDLE in Kernel Config                         |    |

|   | 3.4 Add EXT4 rootfs Support                                   |    |

|   | 3.5 Let Linux Use EXT4 rootfs During Boot                     |    |

|   | 3.6 Build PetaLinux Image                                     |    |

|   | 3.7 Create Petalinux SDK                                      |    |

|   | 3.8 Copy Files for Extensible Platform                        |    |

|   | 3.9 Create Extensible Platform zip File                       |    |

|   | 3.10 Generation of SYSROOT                                    |    |

|   | 3.11 Generation of Extensible Platform for Vitis              |    |

| 4 | Platform Usage                                                |    |

|   | 4.1 Read Platform Info                                        |    |

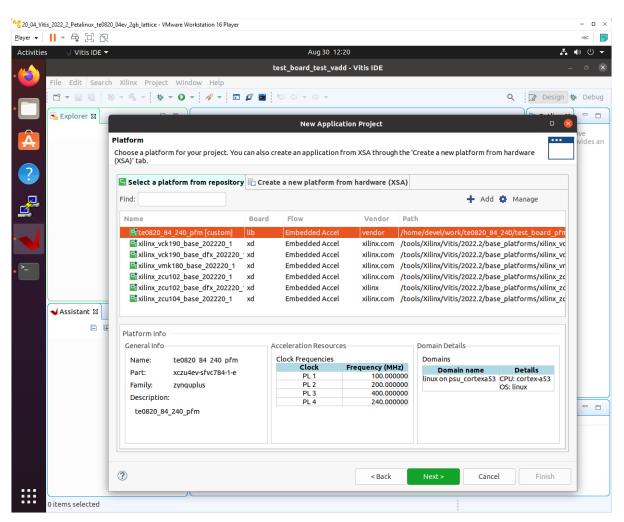

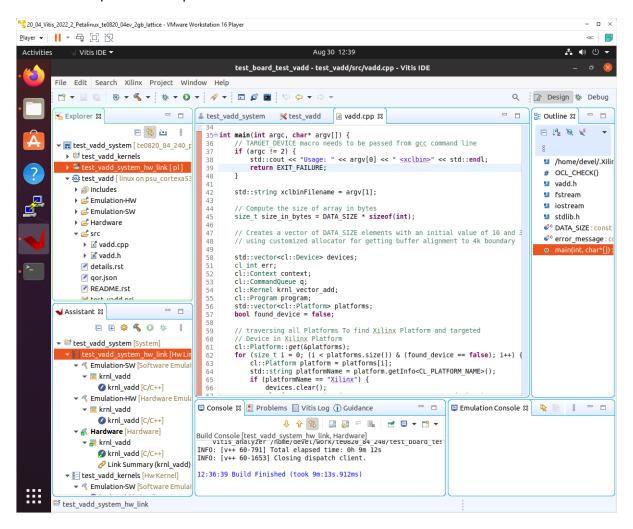

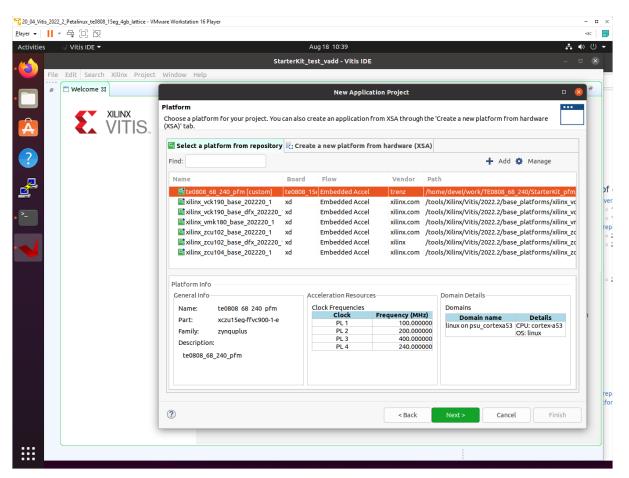

|   | 4.2 Create and Compile Vector Addition Example                |    |

| _ | 4.3 Run Compiled test_vadd Example Application                |    |

| 5 | Vitis AI 3.0 DPUCZDX8V_VAI_v3.0 Installation                  |    |

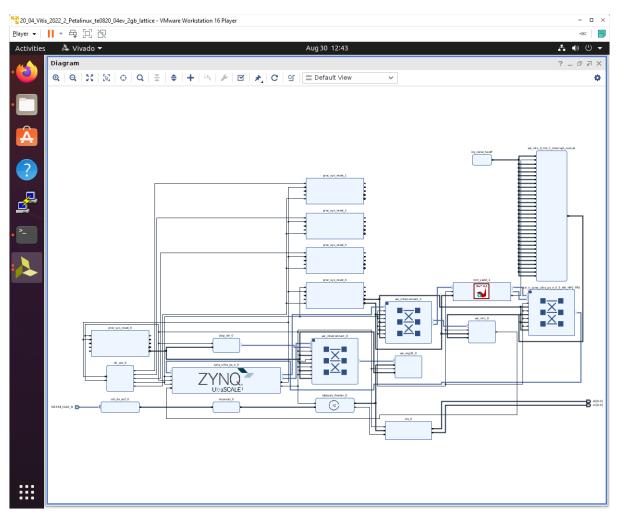

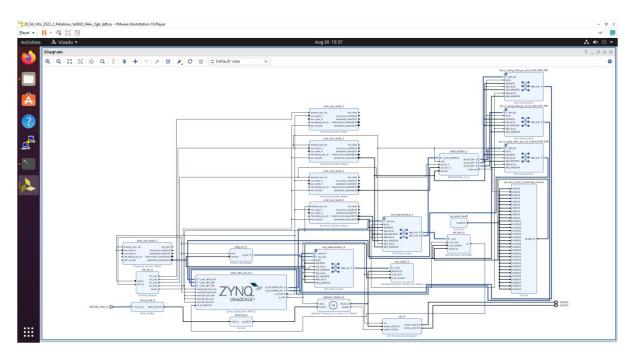

|   | 5.1 Create and Build Vitis Design.                            |    |

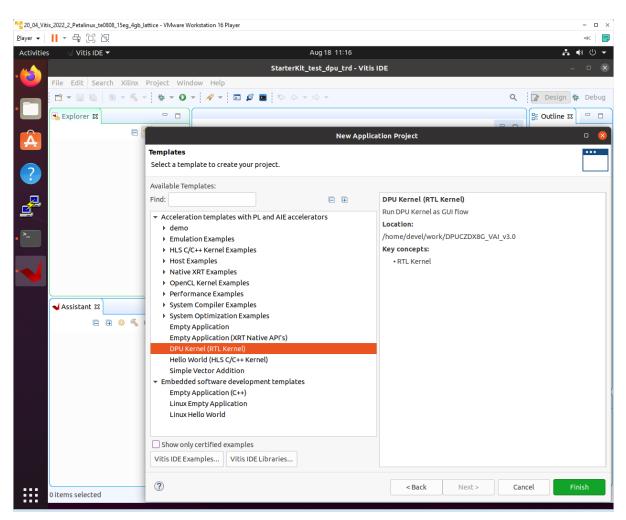

|   | 5.2 Add DPU Project template to the Vitis Extensible Flow     |    |

|   | 5.3 Configure Project for the Vitis Extensible Flow with DPU  |    |

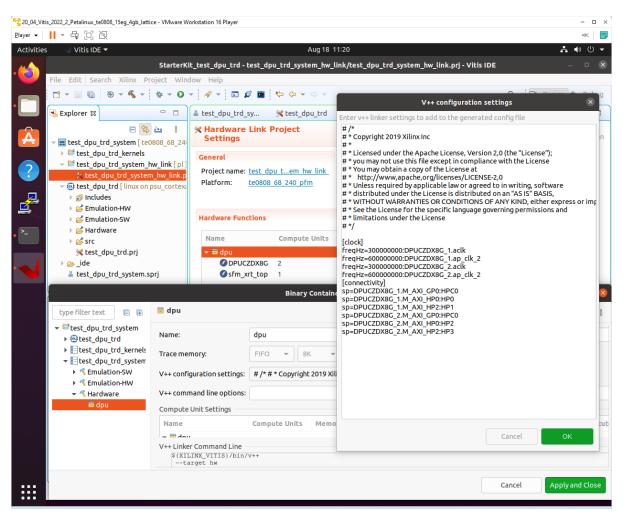

|   | 5.4 Configure Connection of DPU kernel                        |    |

| ~ | 5.5 Build the test_dpu_trd Project                            |    |

| 6 | Prepare SD card with test_dpu_trd DPU                         | 50 |

|   | 6.1 Resize EXT4 Partition                                     |    |

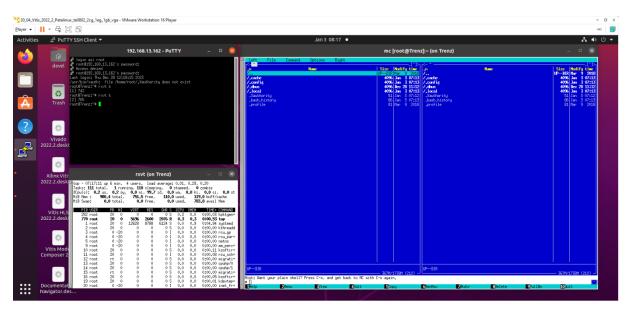

|   | 6.2 Test the Integrated DPUCZDX8G                             | 51 |

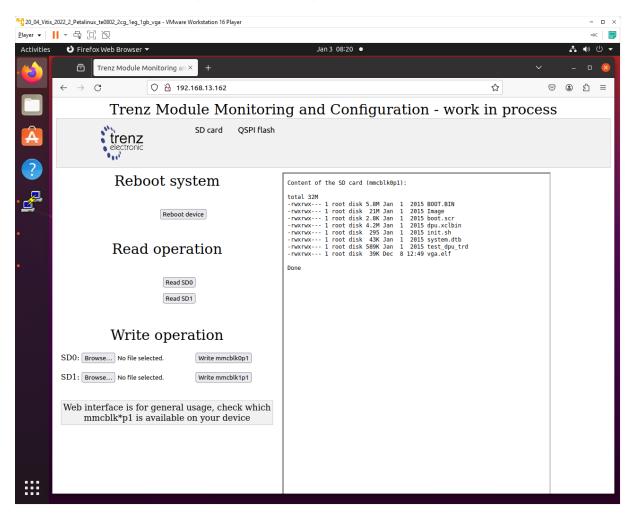

|   | 6.3 Remote Monitoring and Configuration Support               |    |

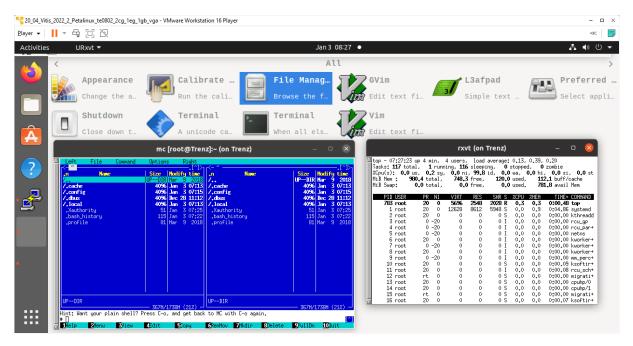

|   | 6.4 Remote Control from Ubuntu X11 Desktop.                   | 54 |

|   | 6.5 Remote Control in x-session-manager on Ubuntu X11 Desktop | 54 |

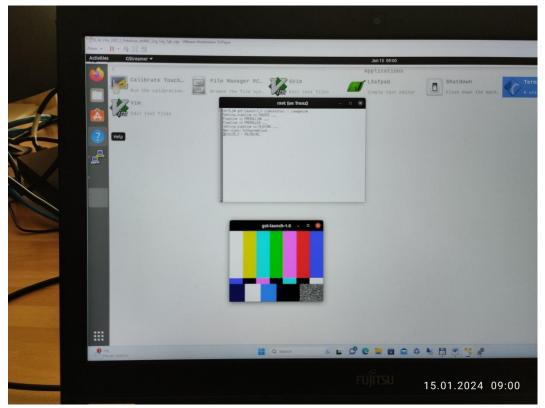

|   | 6.6 Display Test Pattern and Test USB Camera                  | 55 |

|   | 6.7 Vitis AI 3.0 TE0821-01-2AE31KA, TE0701-06, DPU (B1024)    |    |

|   | 6.8 Vitis AI 3.0 TE0821-01-3AE31KA, TE0701-06, DPU (B1600)    |    |

| 7 | 6.9 Vitis AI 3.0 TE0821-01-3BE21FA, TE0701-06, DPU (B1600)    |    |

| 7 | References                                                    | 01 |

ŪTIA

### Acknowledgement

The EECONE project is supported by the Chips Joint Undertaking and its members, including the top-up funding by National Funding Authorities from involved countries under grant agreement no. 101112065.

https://zs.utia.cas.cz/index.php?ids=projects/eecone

https://eecone.com/eecone/home/

https://sp.utia.cas.cz

iii

# 1 Introduction

EECONE project <u>https://eecone.com/eecone/home/</u> work package 4, task 4.3 is investigating measures to support second life of electronics due to modular design.

Work package 4 task 4.4 is investigating measures to support extension of life of electronics due to methodology of support used custom platform to adapt for the in-time-evolving design tools and embedded Linux PetaLinux operating system.

UTIA AV CR, v.v.i. (Institute of Information Theory and Automation of the Czech Academy of Sciences, in short UTIA) is not-for profit research institute located in Prague, Czech Republic. UTIA is involved as partner in both tasks, T4.3 and T4.4.

Both EECONE task require specification of comparable reference systems which are based on modular HW with potential for "second life" by reuse of modules or use cost optimized PCB HW without modularity.

Systems (with HW modularity or low cost single PCB) should be capable to perform similar challenging tasks. Systems have to be capable to accelerate in HW AI inference algorithms with video camera input for edge application like person detection, face detection, car-make or car-type detection and graphical output to local display or to the remote PC connected by wired Ethernet in a local network.

Systems should also support remote monitoring and control from remote PC connected by wired Ethernet in a local network.

The investigated measures and methodologies to support "second life" of electronic modules (T4.3) and measures to support extension of life of electronics (T4.4) due to methodology of support used custom platform to adapt for the in-time-evolving design tools and embedded Linux PetaLinux operating system. We target developers designing the final commercial, Al inference based edge applications, mainly in the area of home automation.

Based on these requirements UTIA have selected two types of systems:

- Low cost systems. See [2], [3]

- Modul based systems. See [4] and [5]. [4] is this application note.

Both compared types of systems use STMicroelectronic STM32H573I-DK board for:

- local system control on small graphical touch screen display

- remote system control from www browser based on www-server or secure communication based on mqtt client. Board is supported by STMicroelectronic CubeMX SW framework and also by NetXDuo SW framework on top of ThreadX OS and FileX SW package.

The MCU used on STM32H573I-DK board is a 40nm chip with 32 bit ARM M33 MCU operating with 250 MHz clock, 2 MBytes of program flash memory and 640 KBytes of RAM.

Compared systems use 16nm AMD ZynqUltrascale+ device with 64 bit ARM A53 Microprocessor and programmable logic in the same device and Petalinux OS.

- Low-cost systems have an AMD ZynqUltrascale+ device and DDR4 with all peripheral interfaces soldered on a single, low cost PCB

- Module-based systems have an AMD ZynqUltrascale+ device and DDR4 soldered on an 4x5 cm module connected by connectors to a carrier board with all peripheral interfaces

1/61

# 1.1 Low cost systems used by UTIA in EECONE T4.3 and T4.4

| [1] | STM32H573I-DK     | https://www.st.com/en/evaluation-<br>tools/stm32h573i-dk.html                                                                                      | Local or remote<br>system control<br>(www-server or<br>secure mqtt client)<br>for [2], [3]    |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| [2] | TE0802-02-1BEV2-A | https://shop.trenz-<br>electronic.de/en/TE0802-02-<br>1BEV2-A-MPSoC-Development-<br>Board-with-AMD-Zynq-UltraScale-<br>ZU1EG-and-1-GB-LPDDR4?c=474 | AMD Vitis AI 3.0<br>AMD DPU in PL<br>USB camera<br>HD VGA display<br>or remote X11<br>desktop |

| [3] | TE0802-02-2AEV2-A | MPSoC Development Board mit<br>AMD Zyng™ UltraScale+™ ZU2<br>und 1 GB LPDDR4   Trenz<br>Electronic GmbH Online Shop (EN)<br>(trenz-electronic.de)  | AMD Vitis AI 3.0<br>AMD DPU in PL<br>USB camera<br>HD VGA display<br>or remote X11<br>desktop |

2/61

https://sp.utia.cas..cz

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

# 1.2 Module based systems used by UTIA in EECONE T4.3 and T4.4

| [1] | STM32H573I-DK<br>TE0701-06<br>Carrier Board for Trenz<br>Electronic 4 x 5 Modules<br>TE0821 or TE0821 | https://www.st.com/en/evaluation-<br>tools/stm32h573i-dk.html<br>https://shop.trenz-<br>electronic.de/en/TE0701-06-<br>Carrier-Board-for-Trenz-Electronic-<br>4-x-5-Modules?c=261 | Local or remote<br>system control<br>(www-server or<br>secure mqtt client)<br>for [4], [5]<br>Carrier Board for<br>range of 4x5 cm<br>modules [4], [5]. |

|-----|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4] | TE0821 Module:<br><b>17 module types</b><br>(to be supported)                                         | https://shop.trenz-<br>electronic.de/en/Products/Trenz-<br>Electronic/TE08XX-Zynq-<br>UltraScale/TE0821-Zynq-<br>UltraScale/                                                      | AMD Vitis AI 3.0<br>AMD DPU in PL<br>USB camera<br>remote X11<br>desktop                                                                                |

| [5] | TE0820 Module:<br><b>100 module types</b><br>(to be supported)                                        | https://shop.trenz-<br>electronic.de/en/Products/Trenz-<br>Electronic/TE08XX-Zynq-<br>UltraScale/TE0820-Zynq-<br>UltraScale/                                                      | AMD Vitis AI 3.0<br>AMD DPU in PL<br>USB camera<br>remote X11<br>desktop                                                                                |

3/61

https://sp.utia.cas..cz

**UTTA** Akad Ústav

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.  $\ensuremath{\textcircled{}}$  © 2024 ÚTIA AV ČR, v.v.i. All disclosure and/or reproduction rights reserved

This application note [4] and the accompanying evaluation package describe support for systems based on TE0821 modules. It is available for free public download from UTIA server dedicated to UTIA contributions to EECONE project: https://zs.utia.cas.cz/index.php?ids=projects/eecone

It will be also available for free public download in format of an wiki tutorial on Trenz-Electronic wiki server:

<u>https://wiki.trenz-</u> electronic.de/display/PD/Vitis+AI+and+Vitis+Acceleration+Tutorials+with+Trenz+Electronic+ Modules

# 1.3 Objective of This Application Note and Evaluation Package

This application note and the accompanying evaluation package describe system [4].

This application note describes how to design custom HW platform with AMD DPU for Vitis 2022.2 AI 3.0 inference for family of Trenz Electronic modules TE0821 with AMD Zynq Ultrascale+ device.

This application note [5] is using AMD Vitis 2022.2 and PetaLinux 2022 tools installed on Ubuntu 20.04. The described configuration integrated AMD DPU IP, version v4.1.0, with architecture DPUCZDX8G.

Described board configuration can operate as small standalone computer with 1 Gb Ethernet connectivity, and remote X11 desktop. Support package for this application note will be available for public download from [5].

The installed AMD DPU configurations require recompilation of Vitis AI 3.0 examples and inference models in the Vitis AI framework. This compilation process will be described in separate application note [6].

This application supports family of TE0821 modules listed in next tables with ID 1 to 17.

Vitis AI 3.0 sample application results are presented for these modules:

- ID=1 module: TE0821-01-2AE31KA, device xczu2cg-sfvc784-1-e, 4GB DDR4

- ID=3 module: TE0821-01-3AE31KA, device xczu3cg-sfvc784-1-e, 4GB DDR4

- ID=5 module: TE0821-01-3BE21FA, device xczu3eg-sfvc784-1-e, 2GB DDR4

Module TE0821-01-2AE31KA has two A53 ARM cores and 4 GB DDR4. It is possible to implement configurations of the AMD DPU (from B512 up to B1024) in PL. Implementation of B1024 is demonstrated.

Module TE0821-01-3AE31KA has two A53 ARM cores and 4 GB DDR4. It is possible to implement configurations of the AMD DPU (from B512 up to B1600) in PL. Implementation of B1600 is demonstrated.

Module TE0821-01-3BE21FA has four A53 ARM cores and 2 GB DDR4. It is possible to implement configurations of the AMD DPU (from B512 up to B1600) in PL. Implementation of B1600 is demonstrated.

department of signal processing

4/61

https://sp.utia.cas..cz

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

Specification for each module ID defined in TE0821\_board\_files.csv file is input to the Vivado 2022.2 HW bring-up scripts. Is provided by company Trenz Electronic. It is part of the package provided for complete family of modules TE0821 for AMD Vivado 2022.2.

List of supported TE0821 modules is reprinted from TE0821\_board\_files.csv file included in the evaluation package associated of this application note.

This application note and associated evaluation package enables support for "second-life" of 17 types of TE0821 modules.

Modules mighed have been used originally in another context. That context might become obsolete or outdated, now. We provide support for reuse of such modules again in a large and challenging range of Vitis AI 3.0 HW accelerated applications.

|    |                   |                     |                                   | SHORTNAM   |                       |                                 | DCD D | DDR       |               | EMM        |

|----|-------------------|---------------------|-----------------------------------|------------|-----------------------|---------------------------------|-------|-----------|---------------|------------|

| ID | PRODID            | PARTNAME            | BOARDNAME                         | E          | ZYNQFLASHTYP          | FPGAFLASHTYP                    | EV    | _SIZ<br>E | FLASH<br>SIZE | C_SIZ<br>E |

| 1  | TE0821-01-2AE31KA | xczu2cg-sfvc784-1-e | trenz.biz:te0821 2cg 1e:part0:3.0 | 2cg 1e 4gb | qspi-x8-dual parallel | mt25qu512-qspi-x8-dual parallel | REV01 | 4GB       |               | 64GB       |

| 2  | TE0821-01-2AE31PA | xczu2cg-sfvc784-1-e | trenz.biz:te0821_2cg_1e:part0:3.0 | 2cg_1e_4gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 4GB       | 128MB         | 64GB       |

| 3  | TE0821-01-3AE31KA | xczu3cg-sfvc784-1-e | trenz.biz:te0821_3cg_1e:part0:3.0 | 3cg_1e_4gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 4GB       | 128MB         | 64GB       |

| 4  | TE0821-01-3AE31PA | xczu3cg-sfvc784-1-e | trenz.biz:te0821_3cg_1e:part0:3.0 | 3cg_1e_4gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 4GB       | 128MB         | 64GB       |

| 5  | TE0821-01-3BE21FA | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:2.0 | 3eg_1e_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 6  | TE0821-01-3BE21FC | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:2.0 | 3eg_1e_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 7  | TE0821-01-3BE21FL | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:2.0 | 3eg_1e_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 8  | TE0821-01-3BE21MA | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:2.0 | 3eg_1e_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 9  | TE0821-01-3BE21ML | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:2.0 | 3eg_1e_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 10 | TE0821-01-3BE91ND | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:3.0 | 3eg_1e_4gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 4GB       | 128MB         | 32GB       |

| 11 | TE0821-01-3BI21FA | xczu3eg-sfvc784-1-i | trenz.biz:te0821_3eg_1i:part0:2.0 | 3eg_1i_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 12 | TE0821-01-3BI21FL | xczu3eg-sfvc784-1-i | trenz.biz:te0821_3eg_1i:part0:2.0 | 3eg_1i_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 13 | TE0821-01-3BI21MA | xczu3eg-sfvc784-1-i | trenz.biz:te0821_3eg_1i:part0:2.0 | 3eg_1i_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 14 | TE0821-01-4DE31FL | xczu4ev-sfvc784-1-e | trenz.biz:te0821_4ev_1e:part0:3.0 | 4ev_1e_4gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 4GB       | 128MB         | 8GB        |

| 15 | TE0821-01-4DE31ML | xczu4ev-sfvc784-1-e | trenz.biz:te0821_4ev_1e:part0:3.0 | 4ev_1e_4gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 4GB       | 128MB         | 8GB        |

| 16 | TE0821-01-S003    | xczu3eg-sfvc784-1-e | trenz.biz:te0821_3eg_1e:part0:2.0 | 3eg_1e_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

| 17 | TE0821-01-S004    | xczu3cg-sfvc784-1-i | trenz.biz:te0821_3cg_1i:part0:2.0 | 3cg_1i_2gb | qspi-x8-dual_parallel | mt25qu512-qspi-x8-dual_parallel | REV01 | 2GB       | 128MB         | 8GB        |

Supported modules with  $ID = 1 \dots 17$

# 2 Prepare Reference Design for Extensible Custom Platform

The design proces is described on module with ID=3: TE0821-01-3AE31KA has two A53 ARM cores and 4 GB DDR4. If your module has different ID, replace 3 with that ID.

In Ubuntu terminal, source paths to Vitis and Vivado tools by

\$ source /tools/Xilinx/Vitis/2022.2/settings64.sh

Download TE0821 test\_board Linux Design file(see Reference Design download link on chapter <u>Requirements</u>) with pre-build files to

~/Downloads/TE0821-test\_board-vivado\_2022.2-build\_8\_20230919135517.zip

This TE0821 test\_board ZIP file contains bring-up scripts for creation of Petalinux for range of modules in zipped directory named "test\_board".

Unzip the file to directory:

~/work/TE0821 3 240

All supported modules are identified in file:

signal processing

5/61

We will select module ID=3 with name TE0821-01-3AE31KA, device xczu3cg-sfvc784-1-e, 4GB DDR4

on TE0701-06 carrier board. We will use default clock 240 MHz. That is why we name the package TE0821\_3\_240 and proposed to unzip the TE0821 test\_board Linux Design files into the directory:

~/work/TE0821 3 240

### 2.1 Reference HW for TE0821 module

In Ubuntu terminal, change directory to the test\_board directory:

\$ cd ~/work/TE0821 3 240/test board

Setup the test\_board directory files for a Linux host machine. In Ubuntu terminal, execute:

\$ chmod ugo+rwx ./console/base sh/\*.sh

```

$ chmod ugo+rwx ./_create_linux_setup.sh

```

```

$ ./_create_linux_setup.sh

```

Select option (0) to open Selection Guide and press Enter

| r₁ de                                                                                                                                   | vel@ubuntu: ~/work/te0821_3_240/test_boar                                                                                                                                                                                                                                           | rd C       | ٦ =                  |        | ×   |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|--------|-----|

| h<br>devel@ubuntu:~/work/<br>.sh<br>devel@ubuntu:~/work/<br>Run Design with:                                                            | <pre>te0821_3_240/test_board\$ chmod ugo+<br/>te0821_3_240/test_board\$ chmod ugo+<br/>te0821_3_240/test_board\$ ./_create_<br/>Set design paths<br/>_create_linux_setup.sh<br/>/home/devel/work/te0821_3_240/test_</pre>                                                           | linux      | /_crea<br>_setup<br> | te_lin | _ I |

|                                                                                                                                         | create_linux_setup.cmd<br>TE Reference Design                                                                                                                                                                                                                                       |            |                      |        |     |

| (x) Exit Batch (<br>(0) Module selec<br>(1) Create minim<br>(2) Create maxim<br>(3) (internal or<br>(g) Install Boar<br>(a) Start desig | ntation (Web Documentation)<br>nothing is done!)<br>tion guide, project creation<br>um setup of CMD-Files and exit Batc<br>um setup of CMD-Files and exit Batc<br>ly) Dev<br>d Files from Xilinx Board Store (be<br>n with unsupported Vivado Version (<br>module selection guide): | :h<br>eta) |                      |        |     |

6/61

Select variant 3 from the selection guide, press enter and agree selection

Create Vivado Project with option 1

| Image: mark of the constraint |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For better table view please resize windows to full screen!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Select Module will be done in 2 steps:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Step 1: (select column filter):<br>-Change module list size (for small monitors only), press: 'full' or 'small'<br>-Display current module list, press: 'L' or 'l'<br>-Restore whole module list, press: 'R' or 'r'<br>-Reduce List by ID, press: 'ID' or 'id' or insert ID columns value directly(filt<br>er step is bypassed and id number is used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -Reduce List by Article Number, press: 'AN' or 'an'<br>-Reduce List by SoC/FPGA, press: 'FPGA' or 'fpga'<br>-Reduce List by PCB REV, press: 'PCB' or 'pcb'<br>-Reduce List by DDR, press: 'DDR' or 'ddr'<br>-Reduce List by Flash, press: 'FLASH' or 'flash'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -Reduce List by EMMC, press: 'EMMC' or 'emmc'<br>-Reduce List by Others, press: 'OTHERS' or 'others'<br>-Reduce List by Notes, press: 'NOTES' or 'notes'<br>-Exit without selection, press: 'Q' or 'q'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Please Enter Option:<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

7/61

https://sp.utia.cas..cz

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

| devel@ubuntu: ~/work/t | :e0821_3_240/t                                                                                                      | est_board                                                                                                                                                     | Q ≡                                                                                                                                                                               | _ 0 (                                                                                                                                                                                                                        | 8                                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :                      |                                                                                                                     |                                                                                                                                                               |                                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |

|                        |                                                                                                                     |                                                                                                                                                               |                                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |

| SoC/FPGA Ty<br> Notes  |                                                                                                                     | Flash<br>                                                                                                                                                     |                                                                                                                                                                                   |                                                                                                                                                                                                                              | PC<br>5                                                                                                                                                                                                                                       |

|                        |                                                                                                                     |                                                                                                                                                               |                                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |

| E31KA  xczu3cg-sfv     |                                                                                                                     |                                                                                                                                                               | 3cg_1e_4gb<br> 64GB                                                                                                                                                               | <br> NA                                                                                                                                                                                                                      | RE                                                                                                                                                                                                                                            |

| NA                     |                                                                                                                     | ا<br>                                                                                                                                                         |                                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |

|                        |                                                                                                                     |                                                                                                                                                               |                                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |

| ke to do?              |                                                                                                                     | 0                                                                                                                                                             |                                                                                                                                                                                   |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |

|                        | :<br> SoC/FPGA Ty<br> Notes<br>E31KA  xczu3cg-sfv<br> NA<br>with this device? y<br>ke to do?<br>delivery binary fol | :<br> SoC/FPGA Typ<br> DDR Size<br> Notes<br>E31KA  xczu3cg-sfvc784-1-e<br> 4GB<br> NA<br>with this device? y/N<br>ke to do?<br>delivery binary folder, press | :<br> SoC/FPGA Typ<br> DDR Size  Flash<br> Notes  <br>E31KA  xczu3cg-sfvc784-1-e<br> 4GB  128MB<br> NA  <br>with this device? y/N<br>ke to do?<br>delivery binary folder, press 0 | :<br> SoC/FPGA Typ  SHORT DIR<br> DDR Size  Flash Size EMMC Siz<br> Notes  <br>E31KA  xczu3cg-sfvc784-1-e  3cg_1e_4gb<br> 4GB  128MB  64GB<br> NA  <br>with this device? y/N<br>ke to do?<br>delivery binary folder, press 0 | :<br> SoC/FPGA Typ  SHORT DIR  <br> DDR Size  Flash Size EMMC Size  Others<br> Notes  <br>E31KA  xczu3cg-sfvc784-1-e  3cg_1e_4gb  <br> 4GB  128MB  64GB  NA<br> NA  <br>with this device? y/N<br>ke to do?<br>delivery binary folder, press 0 |

Vivado project will be generated for module with ID=3, name TE0821-01-3AE31KA, device xczu3cg-sfvc784-1-e, 4GB DDR4

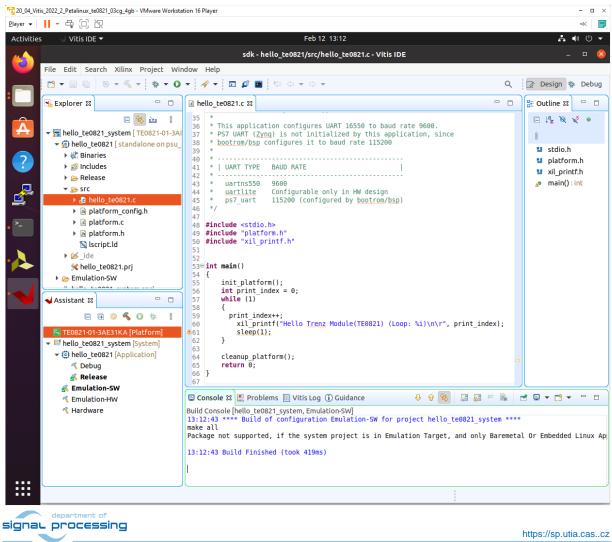

HW support for Vitis Extensible Design Flow

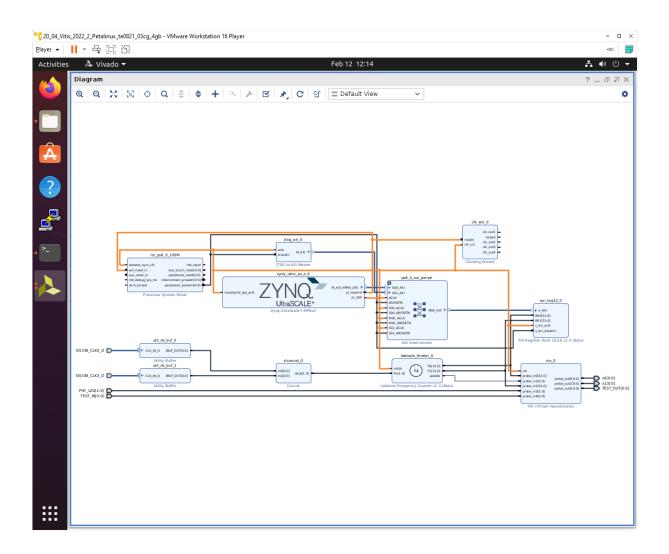

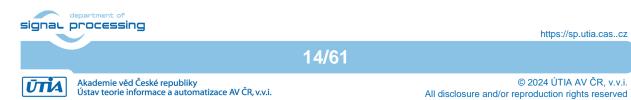

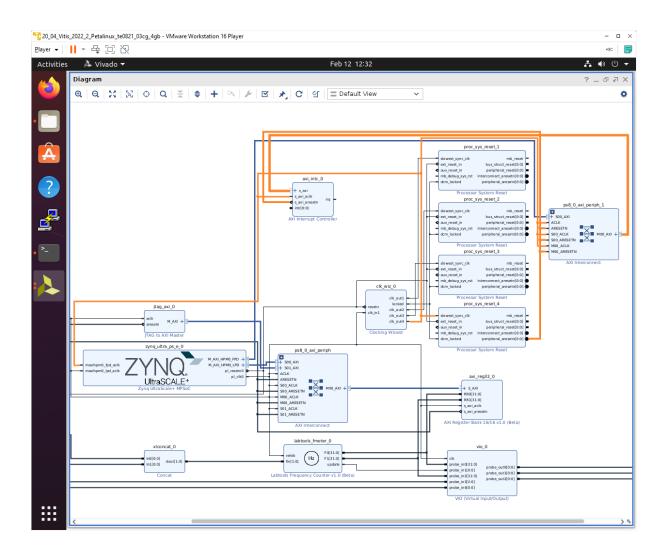

# 2.2 Create Extensible Platform HW

This section describes manual creation of extensible platform HW. You can follow it or you can alternatively use the fast track script described in section 2.3.

In Vivado project, click in **Flow Navigator** on **Settings**. In opened Settings window, select **General** in **Project Settings**, select **Project is an extensible Vitis platform**. Click on **OK**.

8/61

| 5 20_04_Viti     | is_2022_2_Petalinux_te0821_03           | cg_4gb - VMware Workstation 16 Player |                                  |            |                             |                    |                  |                     | - 🗆 ×                               |

|------------------|-----------------------------------------|---------------------------------------|----------------------------------|------------|-----------------------------|--------------------|------------------|---------------------|-------------------------------------|

| <u>P</u> layer ▼ | - 4 🗆 🛛                                 |                                       |                                  |            |                             |                    |                  |                     | « 📄                                 |

| Activities       | s 🔥 Vivado 🔻                            |                                       | Feb 12 1                         | 1:58       |                             |                    |                  | A (                 | 。 () 👻                              |

|                  |                                         | test_board - [/home/devel/wor         | rk/te0821_3_240/test             | :_board/   | vivado/test_board.          | xpr] - Vivado 2022 | 2.2              |                     | • ×                                 |

|                  | <u>F</u> ile <u>E</u> dit F <u>l</u> ow |                                       | Help Q- Quick Acces              | ss         |                             |                    |                  | F                   | Ready                               |

|                  |                                         |                                       | 1/2 B                            | _          |                             |                    | = 0              | Default Layout      | ~                                   |

| •                | Flow Navigator 😤                        |                                       | Setting                          | S          |                             |                    | 8                |                     | ? ×                                 |

|                  | ✓ PROJECT MANAGE                        | Q-                                    |                                  |            |                             |                    |                  |                     | 205                                 |

| Â                | Settings                                | Project Settings                      | General<br>Specify values for va | rious seti | ings used throughou         | t the design flow. |                  | ~                   | •                                   |

|                  | Add Sources                             | General                               | These settings apply             |            |                             | 3                  |                  | •                   | *                                   |

| ?                | Language Temp<br>👎 IP Catalog           | Simulation<br>Elaboration<br>Dataflow | Name:<br>Project device:         | test_bo    | ard<br>R). *SPRT PCB: REV01 | (xczu3ca-sfvc784-1 | -e)              |                     |                                     |

|                  | ✓ IP INTEGRATOR                         | Synthesis                             | Target language:                 | VHDL       |                             |                    | ~                |                     |                                     |

| 2                | Create Block De                         | Implementation<br>Bitstream           | Default library:                 | xil defau  | utlib                       |                    | 0                |                     |                                     |

| _                | Open Block Desi                         | > IP                                  |                                  | zusys w    |                             |                    | 8                |                     |                                     |

| >_               | Generate Block                          | Tool Settings                         | . –                              |            | apper                       |                    | <u>ن</u>         | reg32_0             |                                     |

|                  |                                         | Project                               | Language Option                  | s          |                             |                    |                  |                     |                                     |

|                  | ✓ SIMULATION                            | IP Defaults<br>> Vivado Store         | Verilog options                  | s:         | verilog_version=Veri        | og 2001            |                  | % 16/16 v1.0 (Beta) |                                     |

|                  | Run Simulation                          | Source File                           | G <u>e</u> nerics/Para           | meters:    |                             |                    |                  | /io_0               |                                     |

|                  | ✓ RTL ANALYSIS                          | Display                               | Loop count:                      |            |                             | 1,00               | 0 🗘              |                     | ×0[0:0]                             |

|                  | > Open Elaborate                        | Help<br>> Text Editor                 | _                                |            |                             |                    |                  | =8                  | x0[0:0]<br>x1[0:0]<br>TEST_OUT[0:0] |

|                  |                                         | 3rd Party Simulators                  | ✓ Project is an extension        |            |                             |                    |                  | l'Input/Output)     |                                     |

|                  | ✓ SYNTHESIS                             | > Colors<br>Selection Rules           | Migrate the outp                 | ut produ   | cts to .gen directory s     | tructure           |                  |                     |                                     |

|                  | Run Synthesis                           | Shortcuts                             |                                  |            |                             |                    |                  | -                   |                                     |

|                  | > Open Synthesize                       | > Strategies                          |                                  |            |                             |                    |                  | ?.                  |                                     |

|                  |                                         | > Remote Hosts<br>> Window Behavior   |                                  |            |                             |                    |                  |                     |                                     |

|                  | Run Implementa                          |                                       |                                  |            |                             |                    |                  | -                   | ^_                                  |

|                  | > Open Implement                        |                                       |                                  |            |                             |                    |                  |                     |                                     |

|                  | ✓ PROGRAM AND DEB                       |                                       |                                  |            |                             |                    |                  |                     |                                     |

|                  | 👫 Generate Bitstre                      |                                       |                                  |            |                             |                    |                  |                     |                                     |

|                  | > Open Hardware                         |                                       |                                  |            |                             |                    |                  |                     |                                     |

|                  |                                         | ?                                     |                                  | ОК         | Cancel                      | Apply              | Re <u>s</u> tore | srcs/sources_       | 1/bd/                               |

|                  |                                         | <                                     |                                  |            |                             |                    |                  |                     | >                                   |

|                  |                                         | Type a Tcl command here               |                                  |            |                             |                    |                  |                     |                                     |

|                  | External Port: TEST_OUT                 |                                       |                                  |            |                             |                    |                  |                     |                                     |

IP Integrator of project set up as an extensible Vitis platform has an additional Platform Setup window.

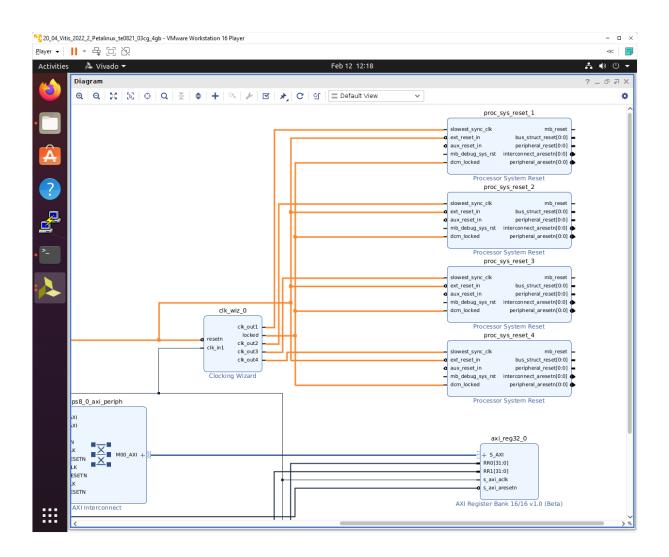

### Add multiple clocks and processor system reset IPs

In IP Integrator Diagram Window, right click, select **Add IP** and add **Clocking Wizard** IP **clk\_wiz\_0**. Double-click on the IP to Re-customize IP window. Select Output Clocks panel. Select four clocks with frequency 100, 200, 400 and 240 MHz. 100 MHz clock will serve as low speed clock.

200 MHz and 400 MHz clock will serve as clock for possible AI engine.

240 MHz clock will serve as the default extensible platform clock. By default, Vitis will compile HW IPs with this default clock.

Set reset type from the default Active High to **Active Low**.

https://sp.utia.cas..cz

ŪTIA

|        | - 4 口 2                                              |                  |              | 10.10.10     |           |            |                       |          | «            |

|--------|------------------------------------------------------|------------------|--------------|--------------|-----------|------------|-----------------------|----------|--------------|

| vities | 🍌 Vivado 🔻                                           |                  |              | 12 12:12     |           |            |                       | Å        | 4) (J        |

|        |                                                      |                  | Re-custo     | mize IP      |           |            |                       | •        | × 0          |

| E      | Clocking Wizard (6.0)                                |                  |              |              |           |            |                       |          | Ready        |

|        |                                                      |                  |              |              |           |            |                       |          |              |

| Fl     | 🚯 Documentation 🛛 🗁 IP Location                      |                  |              |              |           |            |                       |          | 1            |

| Š      |                                                      |                  |              |              |           |            |                       |          | ? 🗆          |

|        | IP Symbol Resource                                   | Component Name   | clk_wiz_0    |              |           |            |                       |          |              |

|        | Show disabled ports                                  | Clocking Options | Output Cl    | ocko MMCN    | 1 Setting | s Summary  |                       |          |              |

|        |                                                      | Clocking Options |              | 3 100.000    |           | 100.00000  | 0.000                 | 0.000 ^  |              |

|        |                                                      | ✓ clk_out2       | -            | 200.000      |           | 200.00000  |                       | 0.000    |              |

|        |                                                      | ✓ clk_out3       | _            | 400.000      | -         | 400.00000  |                       | 0.000    |              |

|        |                                                      | ✓ clk_out4       | clk_out4 (   | 240.000      | 8         | 240.00000  | 0.000 🛞               | 0.000    |              |

|        |                                                      | clk_out5         | clk_out5     | 100.000      |           | N/A        | 0.000                 | N/A      |              |

|        |                                                      | clk_out6         | clk_out6     | 100.000      |           | N/A        | 0.000                 | N/A      | _reg32_0     |

|        |                                                      | clk_out7         | clk_out7     | 100.000      |           | N/A        | 0.000                 | N/A      |              |

| ~      | clk_out1 =<br>clk_out2 =<br>clk_out3 =<br>clk_out3 = |                  |              | ce Number    |           |            |                       |          | <u>via_0</u> |

| ~      |                                                      | clk_out1         | 1            |              | ]         |            |                       |          | al Input/Out |

| Ť      |                                                      | clk_out2         | 1            |              |           |            |                       |          |              |

|        |                                                      | clk_out3         | 1            |              |           |            |                       |          | _ 0          |

|        |                                                      | clk_out4         | 1            |              |           |            |                       |          |              |

| ~      |                                                      | clk_out6         | 1            |              |           |            |                       |          |              |

|        |                                                      | clk_out7         | 1            |              |           |            |                       |          | 1/bd/        |

|        |                                                      |                  |              |              |           |            |                       | U        |              |

| ~      |                                                      | Enable Optional  | Inputs / Out | puts for MMC | M/PLL     | Reset Type |                       | Phase !  |              |

|        |                                                      | ✓ reset          | ) power_down | input_clk    | stopped   | 0.4-44     | ve Hiah () Active Low | 0        | 858 ;        |

|        |                                                      | <                | , power_down | on           | _ccopped  | Activ      | e High ( Active Low   | )'*<br>> |              |

|        |                                                      |                  |              |              |           |            |                       |          | >            |

Clik on OK to close the Re-customize IP window.

Connect input **resetn** of **clk\_wiz\_0** with output **pl\_resetn0** of **zynq\_ultra\_ps\_e\_0**. Connect input **clk\_in1** of **clk\_wiz\_0** with output **pl\_clk0** of **zynq\_ultra\_ps\_e\_0**.

Add and connect four Processor System Reset blocks for each generated clock.

11/61

https://sp.utia.cas..cz

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

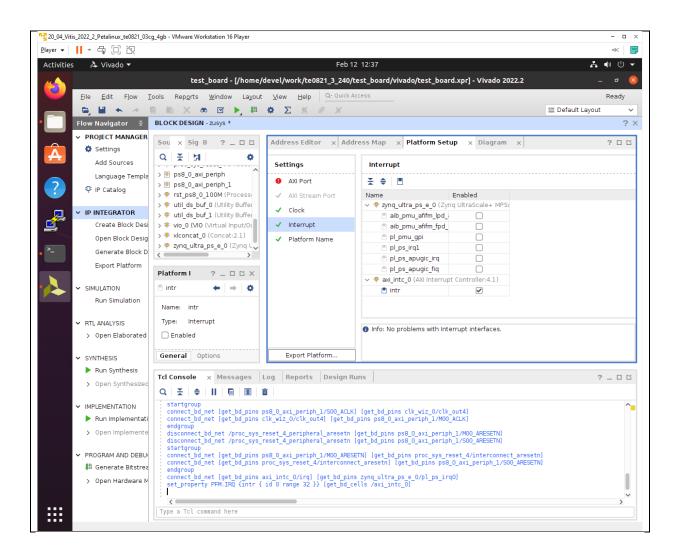

Open Platform Setup window of IP Integrator to define Clocks. In Settings, select Clock.

In "Enabled" column select all four defined clocks clk\_out1, clk\_out2, clk\_out3, clk\_out4 of clk\_wiz\_0 block.

In "ID" column keep the default Clock ID: 1, 2, 3, 4

In "Is Default" column, select **clk\_out4** (with ID=4) as the default clock. One and only one clock must be selected as default clock.

Double-click on **zynq\_ultra\_ps\_e\_0** block and enable **M\_AXI\_HPM0\_FPD** port. Select data width 32bit. It will be used for integration of inerrupt controller on new dedicated AXI stream subsystem with 240 MHz clock. It will also enable new input

pin maxihpm0\_fpd\_aclk of zynq\_ultra\_ps\_e\_0. Connect it to 240 MHz clock net.

Connect input pin **maxihpm0\_fpd\_aclk** of **zynq\_ultra\_ps\_e\_0** to the 240 MHz **clk\_out4** of **clk\_wiz\_0** IP block.

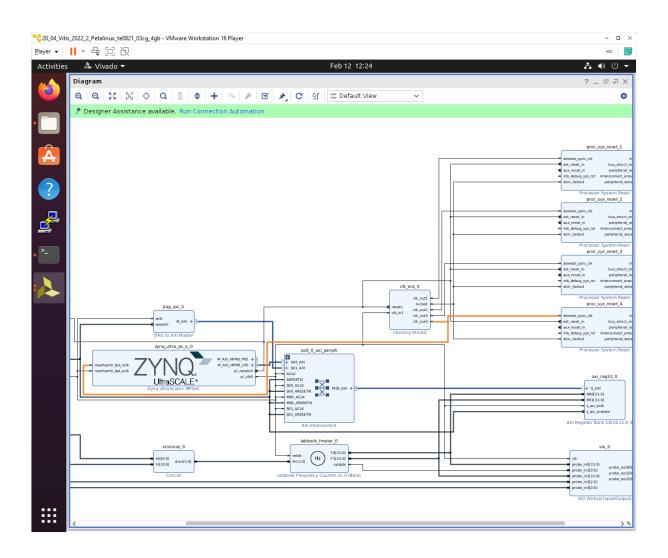

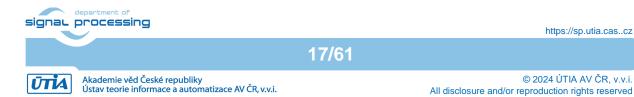

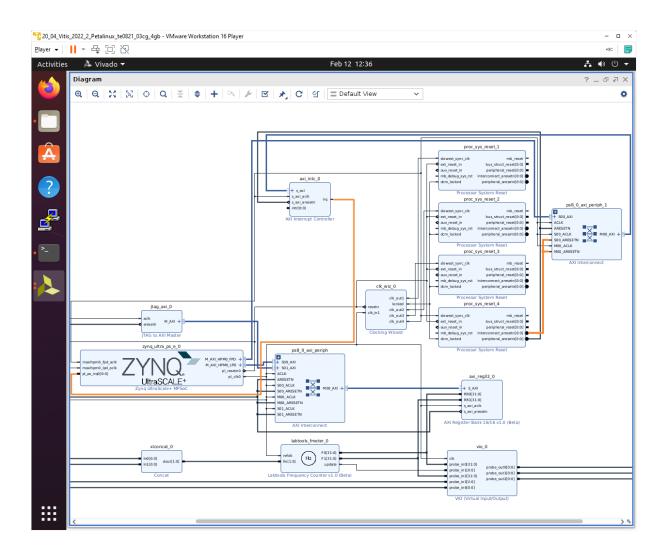

### Add, customize and connect the AXI Interrupt Controller

Add AXI Interrupt Controller IP **axi\_intc\_0**. Double-click on **axi\_intc\_0** to re-customize it.

In "Processor Interrupt Type and Connection" section select the "Interrupt Output Connection" from "Bus" to "Single".

Click on OK to accept these changes.

13/61

https://sp.utia.cas..cz

A

| 5 20_04_Vit      | is_2022_2_Petalinux_te0821_          | 03cg_4gb - VMware Workstation 16 Player |                                                                                   |        | -          | - 🗆 ×        |

|------------------|--------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|--------|------------|--------------|

| <u>P</u> layer ▼ | - 4 2 2                              |                                         |                                                                                   |        | <          | « 📑          |

| Activitie        | s 🔥 Vivado 🔫                         |                                         | Feb 12 12:25                                                                      |        | <b>.</b> ♠ | ७ ◄          |

| -                |                                      | test_board - [/home/dev                 | vel/work/te0821_3_240/test_board/vivado/test_board.xpr] - Vivado 2022.2           |        |            |              |

|                  | <u>F</u> ile <u>E</u> dit Flow       |                                         | Re-customize IP                                                                   |        | Re         | ady          |

|                  |                                      |                                         |                                                                                   | ault I | Layout     | ~            |

| •                | Flow Navigator                       | AXI Interrupt Controller (4.1)          | 4                                                                                 |        |            | ? ×          |

|                  | ✓ PROJECT MANAG                      | Occumentation IP Location               |                                                                                   |        | ?          | 06           |

| Â                | Settings                             |                                         |                                                                                   |        |            | _            |

|                  | Add Sources                          | Show disabled ports                     | Component Name axi_intc_0                                                         |        |            |              |

| ?                | Language Tem                         |                                         |                                                                                   |        |            |              |

|                  | 후 IP Catalog                         |                                         | Basic Advanced Clocks                                                             | ult    | Proc Sy    | Sta          |

|                  | ✓ IP INTEGRATOR                      |                                         | Interrupt Usage                                                                   |        |            |              |

|                  | Create Block D                       |                                         | Number of Peripheral Interrupts (Auto)                                            |        |            | - 11         |

|                  | Open Block De                        |                                         | Fast Interrupt Mode                                                               |        |            |              |

| • >_             | Generate Block                       |                                         | Enable Fast Interrupt Logic                                                       |        |            | -11          |

|                  | Export Platform                      |                                         | Interrupt Vector Address reset value (Auto) 0x00000000000000000000000000000000000 |        | /proc_s    | fixe         |

|                  |                                      |                                         |                                                                                   |        | /proc_s    | fixe         |

|                  | Run Simulation                       |                                         | Peripheral Interrupts Type                                                        |        | /proc_s    | fixe<br>fixe |

|                  | ✓ RTL ANALYSIS                       | + s_axi                                 | Auro Interrupts type - Edge or Level 0xFFFFFFF 0                                  | Ð      |            | ×            |

|                  | <ul> <li>Open Elaboration</li> </ul> | – s_axi_aclk irq –<br>• s_axi_aresetn   | Auro Level type - High or Low 0xFFFFFFF 0                                         |        |            |              |

|                  | , open Lieber et                     | - intr[0:0]                             |                                                                                   |        |            |              |

|                  | ✓ SYNTHESIS                          |                                         | Auro Edge type - Rising or Falling 0xFFFFFFFF 0                                   |        |            | _            |

|                  | Run Synthesis                        |                                         |                                                                                   |        | ? _        |              |

|                  | > Open Synthesi:                     |                                         |                                                                                   |        |            |              |

|                  |                                      |                                         | Processor Interrupt Type and Connection                                           | 100    | 000000"} c | lk_^         |

|                  | Run Implement                        |                                         | Interrupt type Level Interrupt V                                                  | 1000   | 500000 F C | .uk_         |

|                  | > Open Implement                     |                                         | Level type Active High 🗸                                                          |        |            |              |

|                  | ✓ PROGRAM AND DEI                    |                                         | Interrupt Output Connection Single V                                              |        |            |              |

|                  | ↓ <sup>III</sup> Generate Bitst      |                                         |                                                                                   |        |            |              |

|                  | > Open Hardware                      |                                         | <                                                                                 |        |            |              |

|                  |                                      |                                         |                                                                                   |        |            | ~            |

|                  |                                      |                                         | OK Cancel                                                                         |        |            | >            |

| •••              | L                                    |                                         |                                                                                   |        |            |              |

Connect interrupt controller clock input **s\_axi\_aclk** of **axi\_intc\_0** to output **dlk\_out4** of **clk\_wiz\_0**. It is the default, 240 MHz clock of the extensible platform.

### Connect interrupt controller input **s\_axi\_aresetn** of **axi\_intc\_0** to

output **peripheral\_aresetn[0:0]** of **proc\_sys\_reset\_4**. It is the reset block for default, 240 MHz clock of the extensible platform.

Use the **Run Connection Automation** wizard to connect the axi lite interface of interrupt controller **axi\_intc\_0** to master interface **M\_AXI\_HPM0\_FPD** of **zynq\_ultra\_ps\_e\_0**.

| ▼      ▼ 母 [    |                                                                                 |                                                                                        |                                                                    | <ul> <li></li> </ul> |

|-----------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------|

| vities 🍌 Viva   |                                                                                 | Feb 12 12:30                                                                           |                                                                    |                      |

|                 | test_board - [/                                                                 | 'home/devel/work/te0821_3_240/test_bo                                                  | oard/vivado/test_board.xpr] - Vivado 2022.2                        | _ 0                  |

| <u>Eile</u> dit | : F <u>l</u> ow <u>T</u> ools Rep <u>o</u> rts <u>W</u> indow                   | Layout View Help Q- Quick Access                                                       |                                                                    | Ready                |

|                 | ! ■ ! ■ ! X ! @ ! <b>⊠</b> ! ▶                                                  |                                                                                        |                                                                    | 🗮 Default Layout     |

| Flow Navig      |                                                                                 |                                                                                        |                                                                    |                      |

| ✓ PROJECT       | MANAGER                                                                         | T F( Address Editor y Address M                                                        | an                                                                 | ? 🗆                  |

| Set Add         |                                                                                 | Run Connection Auto                                                                    | omation                                                            |                      |

|                 | Automatically make connections in your d<br>configuration options on the right. | lesign by checking the boxes of the interfaces                                         | to connect. Select an interface on the left to displa              | yits 🍌               |

|                 | Q   素   ≑                                                                       | Description                                                                            |                                                                    | y S                  |

| Crea            | All Automation (1 out of 2 selecte<br>v v * axi_intc_0                          | d) Connect Slave interface (/axi_intc_0/                                               | 's_axi) to a selected Master address space.                        |                      |

| Ope             | v ⊕ <mark>s_axi</mark>                                                          | Options                                                                                |                                                                    |                      |

| Ger             | ✓ □ ≢ zynq_ultra_ps_e_0 □ ⊕ M AXI HPM0 FPD                                      | Master interface                                                                       | /zyng ultra ps e 0/M AXI HPM0 FPD ∨                                |                      |

| Ехр             |                                                                                 | Bridge IP                                                                              | New AXI Interconnect                                               | s fi                 |